1. 클럭 (Clock)

우선 클럭 이전에 오실레이터(Osillator)에 대해 간단하게 알아보고 넘어가자.

발진기라고도 부르며 보통 수정(quartz) 결정으로 많이 만들어서 결정 진동자(crystal oscillator)라고도 부른다.

오실레이터에 전기를 가해 역압전 효과(물리적 변형)을 일으켜 규칙적으로 진동을 일으켜 주파수를 발생시키는데 이것을 클럭(Clock)이라고 한다.

오실레이터는 공급 전력이나 온도에 민감하기 때문에 대개 메인보드에 위치하고 있으며, 여기서 내보내는 주파수(Hz)를 얼마나 견딜 수 있는지가 CPU, GPU의 제품 스펙으로 사용된다.

클럭은 연주회의 지위자로 비유할 수 있으며, 일정한 속도로 논리회로의 입출력을 제어하는 역할을 한다.

오버클럭은 말 그대로 지휘를 더욱 빠르게 해서 처리 속도를 늘리겠다는 뜻이다.

또한, 논리회로가 감당할 수 있는 최대 클럭 속도는 회로의 전파 지연 속도에 의해 결정된다.

* 참고 : 논리회로 뿐 아니라 컴퓨터 부품은 우리가 상상하기도 힘들만큼 미세하기 때문에 똑같은 공정에서 생산해도 부품의 편차가 심하다. 그래서 "비닝(binning)"과정이라는 것을 거치는데, 부품을 측정해서 성능이 떨어지는(예를 들자면 지연시간이 오래 걸리는) 제품은 하품, 평범한 제품은 중등품, 우수한 제품은 상등품 이런 식으로 분류하는 것이다.

대표적으로 m1맥북을 보면 같은 칩셋인데도 가격대에 따라 코어 개수가 다른 것을 볼 수 있다.

아래 CPU들은 모두 i9-10900을 만들며 생산된 부산물들이다.

무려 19가지다.

물론 본문에도 나와있듯, 상등품을 많이 생산했으나 메인스트림 모델이 잘 팔릴 경우 임의로 상등품의 일부 기능을 제거하고 메인스트림 모델로 판매할 수도 있다.

https://www.techspot.com/article/2039-chip-binning/

Explainer: What is Chip Binning?

You just bought a new CPU and it seems to run cool, so you try a bit of overclocking. The GHz climbs higher. Did you hit the...

www.techspot.com

2. 래치와 프리플롭, 카운터

(1) 래치

이전의 논리 회로들은 아쉽게도 신호를 기록할 방법이 없었다.

물론 그냥 출력으로 가는 신호를 다시 끌어서 나의 입력으로 가져오는 회로를 만들어버리면 기억이야 할 수 있겠지만, 다시 0으로 바꿀 방법이 없다.

따라서 이렇게 연결한다.

참고로 이 기호는 NAND 게이트로 모든 입력이 참일 때 거짓을 내보내는 회로다.

( 0, 0 => 1 1, 1 => 0 0, 1 => 1 1, 0 => 1 )

우선 회로를 따라가며 경우의 수를 파악해보자.

1. S = 0 R = 0

-> S가 0이 들어가면 두 출력이 하나라도 거짓일 경우 참을 나타내기 때문에 Q는 1을 반환한다.

-> R에 1이 들어가지만 어차피 R이 0이기 때문에 Q1에도 1이 반환된다.

-> Q1이 다시 위의 NAND게이트로 0을 반환하고 계속해서 이 과정이 반복된다.

2. S = 0 R = 1

-> S가 0이 들어가면 두 출력이 하나라도 거짓일 경우 참을 나타내기 때문에 Q는 1을 반환한다.

-> R에 1이 들어갔기 때문에 (1, 1)로 Q1에는 0이 반환된다.

-> 하지만 어차피 S가 0이기 때문에 Q는 다시 1을 반환하고 이것을 무한 반복한다.

이런 식으로 래치가 기존 값을 기억하고 있다는 사실을 알 수 있다.

다음으로는 제어장치가 있는 S-R래치 (Gated S-R Latche)다.

게이트가 있는 래치에서 gete(ENABLE)의 입력값이 1이면 이전과 같은 역할을 수행하지만 0이라면 R과 S에 무엇이 오든 어차피 게이트 입력값은 0이기 때문에 출력이 그대로 유지된다.

그리고 위의 래치를 개선하여 1비트를 저장할 수 있도록 개선한 구조이다. (D는 데이터를 의미하며, 이 래치의 이름은 D-Latch이다.)

드디어 E가 켜져있는 동안(참) D가 1이면 Q에 1이 출력된다.

그러나 여기에는 작은 문제가 있는데, E가 켜져 있는 동안 D가 상태를 바꾸면 그게 모두 출력으로 나타나버리는 것이다.

따라서 신호가 안정된 상태로 전달되기만을 바라며 기도할 수는 없는 법이니 새로운 구조가 만들어졌다.

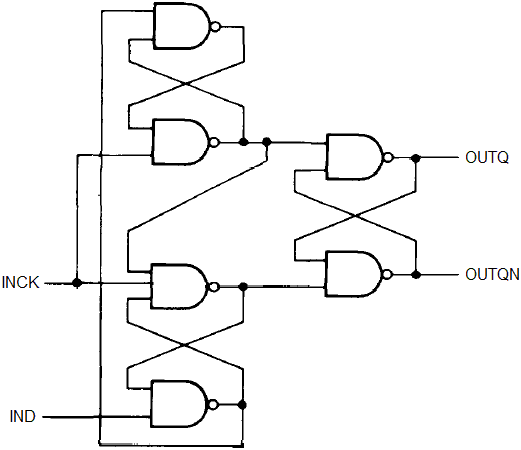

(2) 프리플롭 (Flip-flop)

" 논리 수준이 특정 값에 머무는 동안 데이터를 잡아내지 않고 논리 수준이 한 수준에서 다른 수준으로 전이되는 중간에 데이터를 잡아내는 것"

비전공자 입장에서는 기절할 것 같은 문장 구성이라고 할 수 있겠다.

쉽게 설명하면 CK(클럭)이 1일 때만 D의 값에 의해 출력 값이 변경되며, CK가 0이 되면 D의 값이 어떻게 변하든 더이상 출력값인 OUTQ의 값은 변하지 않는다.

즉, 한 번의 클럭당 정확히 1번의 비트만 입력 받는 것이다.

이유가 궁금하다면 그리 어렵지 않으니 위에서 설명한 것처럼 각각 0, 1을 대입해서 써보면 좋다.

참고로 한 번쯤 들어봤을만한 Register(레지스터)가 바로 플립플롭이 여러개로 구성되어 있는 물건이다.

비싸고 작을 수록 빨라진다는 그래프 말이다.

그리고 Register의 바로 밑에 있는 SRAM 또한 플립플롭으로 만들어진 메모리다.

또한 2개 이상의 플리플롭으로 구성되어 매 클럭 펄스마다 정해진 순서대로 상태가 변하는 논리회로(레지스터)를 카운터라고 부른다.

일반적으로는 아래와 같이 병렬로 연결되어 모든 플리플롭이 동시에 동작하는 동기식 카운터를 주로 사용한다.

카운터의 역할은 타이머, 주파수 계수기로써 클럭의 동작 횟수를 체크하고 플리플롭의 동작 순서를 제어한다. (타이밍 신호를 맞추기 위함)

'CS ﹒ Algorithm > Computer architecture' 카테고리의 다른 글

| 컴퓨터 구조 (7) 중앙처리장치/ 명령어 집합/ 흐름 제어/ RISC/ CISC (0) | 2022.10.03 |

|---|---|

| 컴퓨터 구조 (6) 메모리의 종류와 오류 검출 (Register, RAM, ROM, HDD, Flash) (0) | 2022.09.28 |

| 컴퓨터 구조 (5) 아날로그와 디지털/ 디지털 하드웨어의 역사/ 집적회로(IC)와 논리회로(Logic gate) (0) | 2022.09.19 |

| 컴퓨터 구조 (4) 비트 그룹의 명칭과 다양한 비트 표현(ASCII/ Unicode/ URL/ RGB .. etc) (0) | 2022.08.28 |

| 컴퓨터구조 (3) 이진 실수 표현법(부동 소수점) / 8진법 / 16진법 / BCD / 구별법 (3) | 2022.08.22 |